256Mb Synchronous DRAM based on 4M x 4Bank x16 I/O

# 256M (16Mx16bit) Hynix SDRAM Memory

## **Memory Cell Array**

- Organized as 4banks of 4,194,304 x 16

## **Document Title**

## 256Mbit (16M x16) Synchronous DRAM

## **Revision History**

| Revision No. | History                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Draft Date | Remark      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|

| 0.1          | Initial Draft                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Dec. 2005  | Preliminary |

| 0.2          | Define :<br>Current value (Page 11 ~ 12)                                                                                                                                                                                                                                                                                                                                                                                                                           | Apr. 2006  | Preliminary |

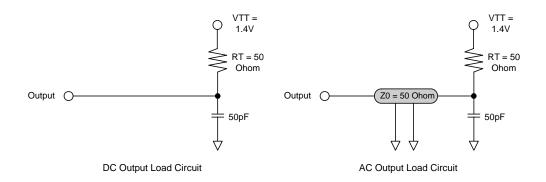

| 0.3          | 1. Cerrect: 1-1. 4Banks x 2Mbits x32> 4Banks x 4Mbits x16(Ordering information; Page 06).  1-2. VDDQ / VSSQ : Power supply for output buffers (Page 08).  2. Remove : Special Power consumption function of Auto TCSR(Temperature Compensated Self Refresh) and PASR(Partial Array Self Refresh).  3. Define : AC Operating TEST condition and AC / DC Output Load circuit (page 10 & 11).  Before :  Output Operation Self-Ac Output Load Circuit (Page 10 & 11). | Jun. 2006  | Preliminary |

| Revision No. | History                                                                                                                                                                                                                                                                                                                                                                                                        | Draft Date | Remark      |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|

| 0.3          | After:  Output O  DC Output Load Circuit  4. Specification change:  4-1. IOH / IOL (Page 11) Before: -2 / 2mA> After: -4 / 4mA.  4-2. tDH, tAH, tCKH, tCH (Page 13) Before: 1.0ns> After: 0.8ns.                                                                                                                                                                                                               | Jun. 2006  | Preliminary |

| 0.4          | <ol> <li>Delete         <ol> <li>COMMAND TRUTH TABLE for Extended Mode Register (Page15)</li> </ol> </li> <li>Insert         <ol> <li>DQM TRUTH TABLE (Page16)</li> </ol> </li> <li>Specitication change:             <ol> <li>IDD6</li> <li>Before: 3 / 1.5mA&gt; After: 2 / 1mA</li> <li>IDD3N</li> <li>Before: 25mA&gt; After: 30mA</li> <li>CHW / tCLW Change [HY57V561620F(L)T(P)-6x]</li></ol></li></ol> | Jun. 2006  | Preliminary |

| 1.0          | Final Ver.                                                                                                                                                                                                                                                                                                                                                                                                     | Sep. 2006  | Final       |

#### **DESCRIPTION**

The Hynix Synchronous DRAM is suited for advaced-consumer application which use the batteries such as Image displayer application (Digital still camera etc.) and portable applications (portable multimedia player and portable audio player). Also, Hynix SDRAMs is used high-speed consumer applications. Short for Hynix Synchronous DRAM, a type of DRAM that can run at much higher clock speeds memory.

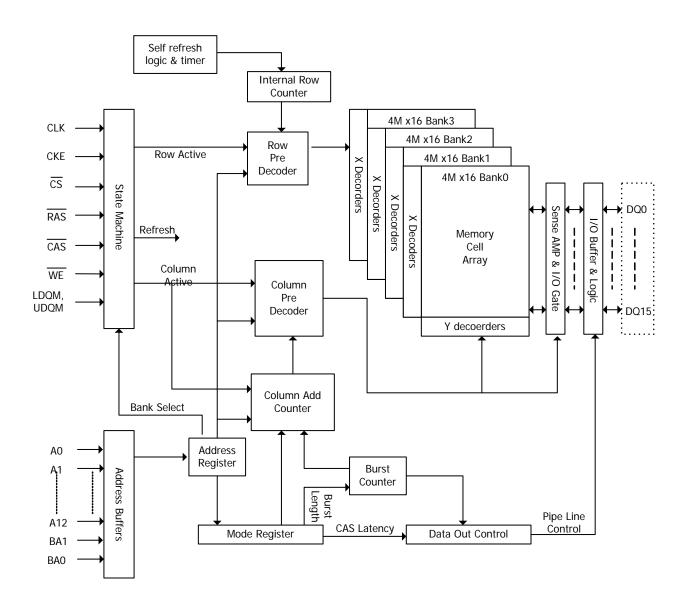

The Hynix HY57V561620F(L)T(P) Synchronous DRAM is 268,435,456bit CMOS Synchronous DRAM, ideally suited for the consumer memory applications which requires large memory density and high bandwidth. It is organized as 4banks of  $4,194,304 \times 16 \text{ I/O}$ .

Synchronous DRAM is a type of DRAM which operates in synchronization with input clock. The Hynix Synchronous DRAM latch each control signal at the rising edge of a basic input clock (CLK) and input/output data in synchronization with the input clock (CLK). The address lines are multiplexed with the Data Input/ Output signals on a multiplexed x16 Input/ Output bus. All the commands are latched in synchronization with the rising edge of CLK.

The Synchronous DRAM provides for programmable read or write Burst length of Programmable burst lengths: 1, 2, 4, 8 locations or full page. An AUTO PRECHARGE function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access. The Synchronous DRAM uses an internal pipelined architecture to achieve high-speed operation. This architecture is compartible with the 2n rule of prefetch architectures, but it also allows the column address to be changed on every clock cycle to achieve a high-speed, fully random access. Precharging one bank while accessing one of the other three banks will hide the precharge cycles and provide seamless, high-speed, randon-access operation.

Read and write accesses to the Hynix Synchronous DRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and the row to be accessed. The address bits registered coincident with the READ or WRITE command are used to select the bank and the starting column location for the burst access.

All inputs are LVTTL compatible. Devices will have a VDD and VDDQ supply of 3.3V (nominal).

## 256Mb Synchronous DRAM(16M x 16) FEATURES

- Standard SDRAM Protocol

- Internal 4bank operation

- Power Supply Voltage: VDD = 3.3V, VDDQ = 3.3V

- All device pins are compatible with LVTTL interface

- Low Voltage interface to reduce I/O power

- 8,192 Refresh cycles / 64ms

- Programmable CAS latency of 2 or 3

- Programmable Burst Length and Burst Type

- 1, 2, 4, 8 or full page for Sequential Burst

- 1, 2, 4 or 8 for Interleave Burst

- 0°C ~ 70°C Operation

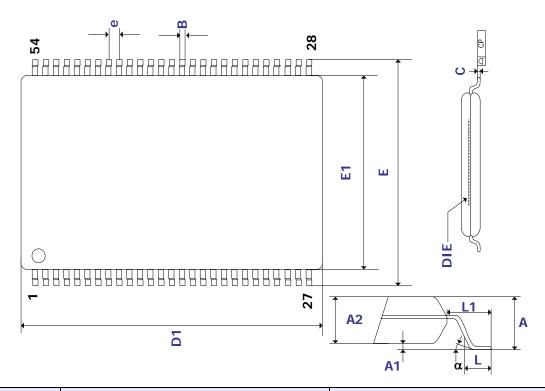

- Package Type: 54\_Pin TSOPII (Lead Free, Lead)

HY57V561620F(L)TP Series: Lead Free

HY57V561620F(L)T Series: Leaded

#### ORDERING INFORMATION

| Part Number       | Clock<br>Frequency | CAS<br>Latency | Power           | Voltage | Organization    | Interface | 54Pin<br>TSOP |        |

|-------------------|--------------------|----------------|-----------------|---------|-----------------|-----------|---------------|--------|

| HY57V561620FT-6   | 166MHz             | 3              | Normal          |         |                 |           |               |        |

| HY57V561620FT-H   | 133MHz             | 3              | INOITHAL        | Normai  |                 |           |               | Leaded |

| HY57V561620FT-6   | 166MHz             | 3              | Low             |         |                 |           | Leaded        |        |

| HY57V561620FLT-H  | 133MHz             | 3              | Power<br>Normal | 3.3V    | 4Banks x 4Mbits | LVTTL     |               |        |

| HY57V561620FTP-6  | 166MHz             | 3              |                 | 3.3V    | x16             | LVIIL     |               |        |

| HY57V561620FTP-H  | 133MHz             | 3              | Normai          |         |                 |           | Lead          |        |

| HY57V561620FLTP-6 | 166MHz             | 3              | Low             |         |                 |           | Free          |        |

| HY57V561620FLTP-H | 133MHz             | 3              | Power           |         |                 |           |               |        |

#### Note:

- 1. HY57V561620FT(P) Series: Normal power 2. HY57V561620FLT(P) Series: Low Power

- 3. HY57V561620F(L)T Series: Leaded 54Pin TSOPII 4. HY57V561620F(L)TP Series: Lead Free 54Pin TSOPII

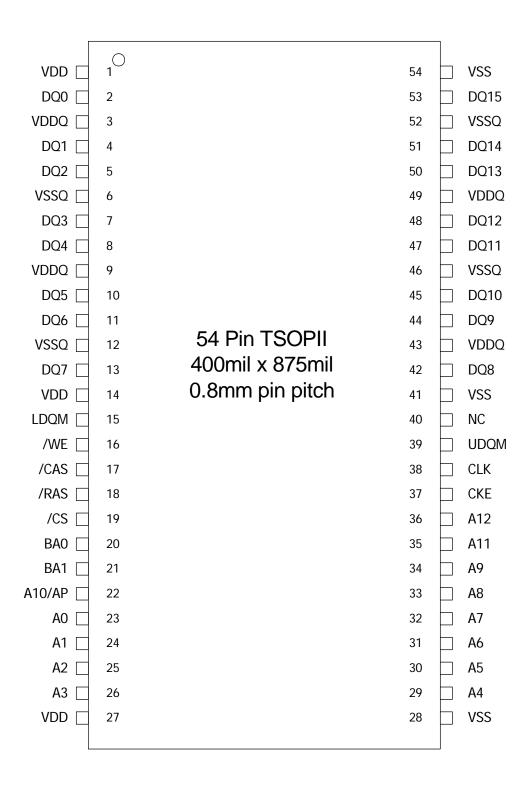

#### **54 TSOP II Pin ASSIGNMENTS**

## **54\_TSOPII Pin DESCRIPTIONS**

| SYMBOL        | TYPE   | DESCRIPTION                                                                                                                                            |

|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK           | INPUT  | Clock : The system clock input. All other inputs are registered to the SDRAM on the rising edge of CLK                                                 |

| CKE           | INPUT  | Clock Enable:<br>Controls internal clock signal and when deactivated, the SDRAM will be one of the states<br>among power down, suspend or self refresh |

| <del>cs</del> | INPUT  | Chip Select: Enables or disables all inputs except CLK, CKE and DQM                                                                                    |

| BAO, BA1      | INPUT  | Bank Address: Selects bank to be activated during RAS activity Selects bank to be read/written during CAS activity                                     |

| A0 ~ A12      | INPUT  | Row Address: RA0 ~ RA12, Column Address: CA0 ~ CA8<br>Auto-precharge flag: A10                                                                         |

| RAS, CAS, WE  | INPUT  | Command Inputs:  RAS, CAS and WE define the operation Refer function truth table for details                                                           |

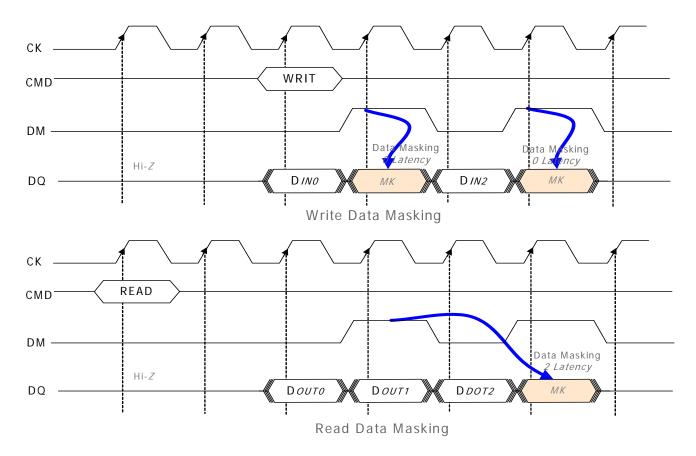

| LDQM, UDQM    | I/O    | Data Mask:<br>Controls output buffers in read mode and masks input data in write mode                                                                  |

| DQ0 ~ DQ15    | I/O    | Data Input / Output:<br>Multiplexed data input / output pin                                                                                            |

| VDD / VSS     | SUPPLY | Power supply for internal circuits and input buffers                                                                                                   |

| VDDQ / VSSQ   | SUPPLY | Power supply for output buffers                                                                                                                        |

| NC            | -      | No connection : These pads should be left unconnected                                                                                                  |

## FUNCTIONAL BLOCK DIAGRAM 4Mbit x 4banks x 16 I/O Synchronous DRAM

#### **ABSOLUTE MAXIMUM RATING**

| Parameter                             | Symbol    | Rating     | Unit |

|---------------------------------------|-----------|------------|------|

| Ambient Temperature                   | TA        | 0 ~ 70     | οС   |

| Storage Temperature                   | TSTG      | -55 ~ 125  | °C   |

| Voltage on Any Pin relative to VSS    | VIN, VOUT | -1.0 ~ 4.6 | V    |

| Voltage on VDD supply relative to VSS | VDD, VDDQ | -1.0 ~ 4.6 | V    |

| Short Circuit Output Current          | IOS       | 50         | mA   |

| Power Dissipation                     | PD        | 1          | W    |

Note: Operation at above absolute maximum rating can adversely affect device reliability

#### DC OPERATING CONDITION

| Parameter            | Symbol    | Min  | Max        | Unit | Note |

|----------------------|-----------|------|------------|------|------|

| Power Supply Voltage | VDD, VDDQ | 3.0  | 3.6        | V    | 1    |

| Input High Voltage   | VIH       | 2.0  | VDDQ + 0.3 | V    | 1, 2 |

| Input Low Voltage    | VIL       | -0.3 | 0.8        | V    | 1, 3 |

**Note:** 1. All voltages are referenced to VSS = 0V.

- 2. VIH(Max) is acceptable VDDQ + 2V for a pulse width with <= 3ns of duration.

- 3. VIL(min) is acceptable -2.0V for a pulse width with <= 3ns of duration.

#### AC OPERATING TEST CONDITION (TA= 0 to 70°C, VDD=3.3±0.3V / VSS=0V)

| Parameter                                           | Symbol    | Value     | Unit | Note |

|-----------------------------------------------------|-----------|-----------|------|------|

| AC Input High / Low Level Voltage                   | VIH / VIL | 2.4 / 0.4 | V    |      |

| Input Timing Measurement Reference Level Voltage    | Vtrip     | 1.4       | V    |      |

| Input Rise / Fall Time                              | tR / tF   | 1         | ns   |      |

| Output Timing Measurement Reference Level Voltage   | Voutref   | 1.4       | V    |      |

| Output Load Capacitance for Access Time Measurement | CL        | 50        | pF   | 1    |

Note: 1. See Next Page

## **CAPACITANCE** (f=1MHz)

| Parameter                       | Pin                                       | Symbol | Min | Max | Unit |

|---------------------------------|-------------------------------------------|--------|-----|-----|------|

|                                 | CLK                                       | CI1    | 2.0 | 4.0 | pF   |

| Input capacitance               | A0 ~ A12, BA0, BA1, CKE, CS, RAS, CAS, WE | CI2    | 2.0 | 4.0 | pF   |

|                                 | LDQM, UDQM                                | CI3    | 2.0 | 4.0 | pF   |

| Data input / output capacitance | DQ0 ~ DQ15                                | CI/O   | 3.5 | 6.5 | pF   |

#### DC CHARACTERRISTICS I (TA= 0 to 70°C)

| Parameter              | Symbol | Min | Max | Unit | Note       |

|------------------------|--------|-----|-----|------|------------|

| Input Leakage Current  | ILI    | -1  | 1   | uA   | 1          |

| Output Leakage Current | ILO    | -1  | 1   | uA   | 2          |

| Output High Voltage    | Voh    | 2.4 | -   | V    | IOH = -4mA |

| Output Low Voltage     | VOL    | -   | 0.4 | V    | IOL = +4mA |

#### Note

- 1. VIN = 0 to 3.6V, All other balls are not tested under VIN = 0V

- 2. DOUT is disabled, VOUT=0 to 3.6

## DC CHARACTERISTICS II (TA= 0 to 70°C)

| Darameter                                         | Parameter Symbol Test Condition |                                                                                                                                                               |             |            | eed | Unit  | Note |   |

|---------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-----|-------|------|---|

| rarameter                                         | Symbol                          | rest condition                                                                                                                                                |             | 6 H        |     | Oiiit | Note |   |

| Operating Current                                 | IDD1                            | Burst length=1, One bank activities $tRC \ge tRC(min)$ , $IOL=0mA$                                                                                            | 100         | 90         | mA  | 1     |      |   |

| Precharge Standby                                 | IDD2P                           | CKE ≤ VIL(max), tCK = 15ns                                                                                                                                    |             | 1          | .0  | mA    |      |   |

| Current<br>in Power Down Mode                     | IDD2PS                          | $CKE \leq VIL(max)$ , $tCK = \infty$                                                                                                                          |             | 1          | .0  | mA    |      |   |

| Precharge Standby<br>Current<br>in Non Power Down | IDD2N                           | CKE $\geq$ VIH(min), $\overline{CS} \geq$ VIH(min), tCK = 15ns Input signals are changed one time during 2clks. All other pins $\geq$ VDD-0.2V or $\leq$ 0.2V |             |            |     | mA    |      |   |

| Mode                                              | IDD2NS                          | $CKE \ge VIH(min)$ , $tCK = \infty$<br>Input signals are stable.                                                                                              | 8           | 3          |     |       |      |   |

| Active Standby Cur-                               | IDD3P                           | CKE ≤ VIL(max), tCK = 15ns                                                                                                                                    |             | 3          |     |       |      |   |

| rent<br>in Power Down Mode                        | IDD3PS                          | $CKE \leq VIL(max)$ , $tCK = \infty$                                                                                                                          | ;           | 3          | mA  |       |      |   |

| Active Standby Current in Non Power Down Mode     | IDD3N                           | CKE $\geq$ VIH(min), $\overline{\text{CS}} \geq$ VIH(min), Input signals are changed one 2clks. All other pins $\geq$ VDD-0.2V or $\leq$                      | time during | 3          | 0   | mA    |      |   |

| Downwood                                          | IDD3NS                          | $CKE \ge VIH(min)$ , $tCK = \infty$<br>Input signals are stable.                                                                                              |             | 2          | 0   |       |      |   |

| Burst Mode Operating<br>Current                   | IDD4                            | tCK ≥ tCK(min), IOL=0mA<br>All banks active                                                                                                                   |             | 100        | 90  | mA    | 1    |   |

| Auto Refresh Current                              | IDD5                            | tRC ≥ tRC(min), All banks active                                                                                                                              | 180         | 170        | mA  | 2     |      |   |

| Self Refresh Current                              | IDD6                            | IDDY CVE < 0.2W                                                                                                                                               |             | Normal 2.0 |     | .0    | mA   | 3 |

| Jen Kenesh Gunent                                 | 1000                            | ONL 3 0.2 V                                                                                                                                                   | Low Power   | 1.0        |     | 111/5 | 3    |   |

Note: 1. IDD1 and IDD4 depend on output loading and cycle rates. Specified values are measured with the output open.

<sup>2.</sup> Min. of tRC (Refresh RAS cycle time) is shown at AC CHARACTERISTICS II

<sup>3.</sup> HY57V561620FT(P) Series: Normal, HY57V561620FLT(P) Series: Low Power

## AC CHARACTERISTICS I (AC operating conditions unless otherwise noted)

| Parameter                        |                       | Symbol | (   | 6    | ŀ   | +    | Unit  | Note |

|----------------------------------|-----------------------|--------|-----|------|-----|------|-------|------|

|                                  |                       | Symbol | Min | Max  | Min | Max  | Offic | Note |

| System Clock Cycle Time          | CL = 3                | tCK3   | 6.0 | 1000 | 7.5 | 1000 | ns    |      |

| System block bythe filling       | CL = 2                | tCK2   | 7.5 | 1000 | 10  | 1000 | ns    |      |

| Clock High Pulse Width           |                       | tCHW   | 2.5 | -    | 2.5 | -    | ns    | 1    |

| Clock Low Pulse Width            |                       | tCLW   | 2.5 | -    | 2.5 | -    | ns    | 1    |

| Access Time From Clock           | CL = 3                | tAC3   | -   | 5.4  | -   | 5.4  | ns    | 2    |

| Access Time From Clock           | CL = 2                | tAC2   | -   | 6    | -   | 6    | ns    | 2    |

| Data-out Hold Time               |                       | tOH    | 2.0 | -    | 2.5 | -    | ns    |      |

| Data-Input Setup Time            | Data-Input Setup Time |        | 1.5 | -    | 1.5 | -    | ns    | 1    |

| Data-Input Hold Time             |                       | tDH    | 0.8 | -    | 0.8 | -    | ns    | 1    |

| Address Setup Time               |                       | tAS    | 1.5 | -    | 1.5 | -    | ns    | 1    |

| Address Hold Time                |                       | tAH    | 0.8 | -    | 0.8 | -    | ns    | 1    |

| CKE Setup Time                   |                       | tcks   | 1.5 | -    | 1.5 | -    | ns    | 1    |

| CKE Hold Time                    |                       | tCKH   | 0.8 | -    | 0.8 | -    | ns    | 1    |

| Command Setup Time               |                       | tCS    | 1.5 | -    | 1.5 | -    | ns    | 1    |

| Command Hold Time                |                       | tCH    | 0.8 | -    | 0.8 | -    | ns    | 1    |

| CLK to Data Output in Low-Z Time |                       | tOLZ   | 1.0 | -    | 1.0 | -    | ns    |      |

| CLK to Data Output in High-Z     | CL = 3                | tOHZ3  | 2.7 | 5.4  | 2.7 | 5.4  | ns    |      |

| Time                             | CL = 2                | tOHZ2  | 2.7 | 5.4  | 3   | 6    | ns    |      |

#### Note:

<sup>1.</sup> Assume tR / tF (input rise and fall time) is 1ns. If tR & tF > 1ns, then [(tR+tF)/2-1]ns should be added to the parameter.

<sup>2.</sup> Access time to be measured with input signals of 1V/ns edge rate, from 0.8V to 0.2V. If tR > 1ns, then (tR/2-0.5)ns should be added to the parameter.

## AC CHARACTERISTICS II (AC operating conditions unless otherwise noted)

| Parameter                       |              | Symbol | (          | 6    |     | 1    | Unit  | Note |

|---------------------------------|--------------|--------|------------|------|-----|------|-------|------|

|                                 |              | Symbol | Min        | Max  | Min | Max  | Oilit | Note |

| RAS Cycle Time                  | Operation    | tRC    | 60         | -    | 63  | -    | ns    |      |

| KAS Cycle Time                  | Auto Refresh | trrc   | 60         | -    | 63  | -    | ns    |      |

| RAS to CAS Delay                |              | tRCD   | 18         | -    | 20  | -    | ns    |      |

| RAS Active Time                 |              | tras   | 42         | 100K | 42  | 100K | ns    |      |

| RAS Precharge Time              |              | trp    | 18         | -    | 20  | -    | ns    |      |

| RAS to RAS Bank Active Delay    |              | trrd   | 12         | -    | 15  | -    | ns    |      |

| CAS to CAS Delay                |              | tCCD   | 1          | -    | 1   | -    | CLK   |      |

| Write Command to Data-In Delay  |              | tWTL   | 0          | -    | 0   | -    | CLK   |      |

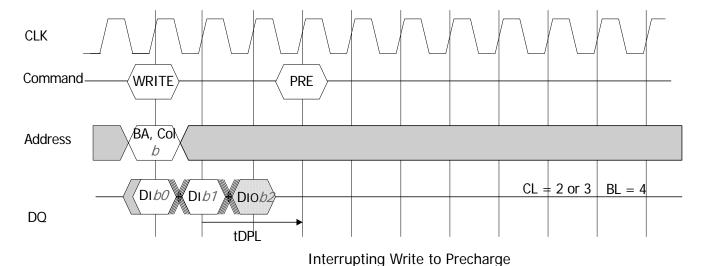

| Data-in to Precharge Command    |              | tDPL   | 2          | -    | 2   | -    | CLK   |      |

| Data-In to Active Command       |              | tDAL   | tDPL + tRP |      |     |      |       |      |

| DQM to Data-Out Hi-Z            |              | tDQZ   | 2          | -    | 2   | -    | CLK   |      |

| DQM to Data-In Mask             |              | tDQM   | 0          | -    | 0   | -    | CLK   |      |

| MRS to New Command              |              | tMRD   | 2          | -    | 2   | -    | CLK   |      |

| Prochargo to Data Output High 7 | CL = 3       | tPROZ3 | 3          | -    | 3   | -    | CLK   |      |

| Precharge to Data Output High-Z | CL = 2       | tPROZ2 | 2          | -    | 2   | -    | CLK   |      |

| Power Down Exit Time            |              | tDPE   | 1          | -    | 1   | -    | CLK   |      |

| Self Refresh Exit Time          |              | tsre   | 1          | -    | 1   | -    | CLK   | 1    |

| Refresh Time                    |              | tref   | -          | 64   | -   | 64   | ms    |      |

$\textbf{Note:} \ \textbf{1.} \ \textbf{A} \ \textbf{new command can be given tRC after self refresh exit.}$

## BASIC FUNCTIONAL DESCRIPTION

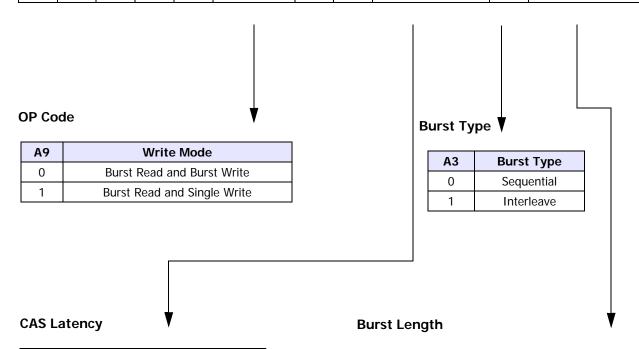

#### **Mode Register**

| BA1 | BA0 | A12 | A11 | A10 | А9      | A8 | Α7         | A6 | <b>A</b> 5 | A4  | А3 | A2 | A1       | Α0  |

|-----|-----|-----|-----|-----|---------|----|------------|----|------------|-----|----|----|----------|-----|

| 0   | 0   | 0   | 0   | 0   | OP Code | 0  | 0 0 CAS La |    | S Later    | ісу | BT | Bu | rst Lenç | gth |

| A6 | <b>A</b> 5 | A4 | CAS Latency |

|----|------------|----|-------------|

| 0  | 0          | 0  | Reserved    |

| 0  | 0          | 1  | Reserved    |

| 0  | 1          | 0  | 2           |

| 0  | 1          | 1  | 3           |

| 1  | 0          | 0  | Reserved    |

| 1  | 0          | 1  | Reserved    |

| 1  | 1          | 0  | Reserved    |

| 1  | 1          | 1  | Reserved    |

| A2 | A1 | AO | Burst I   | _ength   |

|----|----|----|-----------|----------|

| AZ | AI | AU | A3 = 0    | A3=1     |

| 0  | 0  | 0  | 1         | 1        |

| 0  | 0  | 1  | 2         | 2        |

| 0  | 1  | 0  | 4         | 4        |

| 0  | 1  | 1  | 8         | 8        |

| 1  | 0  | 0  | Reserved  | Reserved |

| 1  | 0  | 1  | Reserved  | Reserved |

| 1  | 1  | 0  | Reserved  | Reserved |

| 1  | 1  | 1  | Full page | Reserved |

## **COMMAND TRUTH TABLE**

| Function                  | CKEn-1 | CKEn | cs     | RAS    | CAS    | WE     | DQM | ADDR           | A10<br>/AP         | ВА | Note |

|---------------------------|--------|------|--------|--------|--------|--------|-----|----------------|--------------------|----|------|

| Mode Register Set         | Н      | Х    | L      | L      | L      | L      | Х   | 0              | p Code             |    |      |

| No Operation              | Н      | Χ    | L      | Н      | Н      | Н      | Χ   |                | Χ                  |    |      |

| Device Deselect           | Н      | Χ    | Н      | Χ      | Χ      | Χ      | Χ   |                | Χ                  |    |      |

| Bank Active               | Н      | Χ    | L      | L      | Н      | Н      | Χ   | Row Ad         | ldress             | V  |      |

| Read                      | Н      | Х    | L      | Н      | L      | Н      |     | Col-<br>umn    | L                  | V  |      |

| Read with Autoprecharge   | Н      | Х    | L      | Н      | L      | Н      | Х   | Col-<br>umn    | Н                  | V  |      |

| Write                     | Н      | Х    | L      | Н      | L      | L      | Х   | Col-<br>umn    | L                  | V  |      |

| Write with Autoprecharge  | Н      | Х    | L      | Н      | L      | L      | Х   | Col-<br>umn    | Н                  | V  |      |

| Precharge All Banks       | Н      | Χ    | L      | L      | Н      | L      | Χ   | Х              | Н                  | Χ  |      |

| Precharge selected Bank   | Н      | Χ    | L      | L      | Н      | L      | Χ   | Х              | L                  | V  |      |

| Burst stop                | Н      | Χ    | L      | Н      | Н      | L      | Χ   |                | Χ                  |    |      |

| DQM                       | Н      | Χ    |        | )      | Χ      |        | V   |                | Χ                  |    | 2    |

| Auto Refresh              | Н      | Н    | L      | L      | L      | Н      | Χ   |                | Χ                  |    |      |

| Burst-Read Single-Write   | Н      | Х    | L      | L      | L      | Н      | X   | A9<br>(Other F | Pin Hig<br>Pins OP |    |      |

| Self Refresh Entry        | Н      | L    | L      | L      | L      | Н      | Χ   |                | Χ                  |    |      |

| Self Refresh Exit         | L      | Н    | Н      | Χ      | Χ      | Χ      | Х   |                | Х                  |    | 1    |

| Self Refresh Exit         |        | 11   | L      | Н      | Н      | Н      | ^   |                |                    |    | '    |

| Precharge Power Down      | Н      | L    | Н      | Х      | Х      | Х      | Х   |                | Х                  |    |      |

| Entry                     |        |      | L      | Н      | Н      | Н      | ^   |                |                    |    |      |

| Precharge Power Down Exit | L      | Н    | H<br>L | X<br>H | X<br>H | X<br>H | Х   |                | Χ                  |    |      |

|                           |        | _    | Н      | Х      | Х      | Х      |     |                |                    |    |      |

| Clock Suspend Entry       | Н      | L    | L      | V      | V      | V      | Х   | X              |                    |    |      |

| Clock Suspend Exit        | L      | Н    |        | )      | Χ.     | ı      | Х   |                | Х                  |    |      |

Note: 1. Exiting Self Refresh occurs by asynchronously bringing CKE from low to high. 2. see to Next page (DQM TRUTH TABLE)

## **DOM TRUTH TABLE**

| Function                                                          | CKEn-1 | CKEn | LDQM | UDQM |

|-------------------------------------------------------------------|--------|------|------|------|

| Data Write/Output enable                                          | Н      | Х    | L    | L    |

| Data Mask/Output disable                                          | Н      | Х    | Н    | Н    |

| Lower byte write/Output enable,<br>Upper byte mask/Output disable | Н      | Х    | L    | Н    |

| Lower byte Mask/Output disable,<br>Upper byte write/Output enable | Н      | Х    | Н    | L    |

Note 1. H: High Level, L: Low Level, X: Don't Care 2. Write DQM Latency is 0 CLK and Read DQM Latency is 2 CLK

## CURRENT STATE TRUTH TABLE (Sheet 1 of 4)

| Cummomt          |    |     |     |    |             | Command          |                      |                                                |       |

|------------------|----|-----|-----|----|-------------|------------------|----------------------|------------------------------------------------|-------|

| Current<br>State | cs | RAS | CAS | WE | BAO/<br>BA1 | A <i>max</i> -A0 | Description          | Action                                         | Notes |

|                  | L  | L   | L   | L  |             | OP CODE          | Mode Register Set    | Set the Mode Register                          |       |

|                  | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh | Start Auto or Self Refresh                     | 5     |

|                  | L  | L   | Н   | L  | ВА          | Х                | Precharge            | No Operation                                   |       |

|                  | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate        | Activate the specified bank and row            |       |

| idle             | L  | Н   | L   | L  | ВА          | Col Add.<br>A10  | Write/WriteAP        | ILLEGAL                                        | 4     |

|                  | L  | Н   | L   | Н  | ВА          | Col Add.<br>A10  | Read/ReadAP          | ILLEGAL                                        | 4     |

|                  | L  | Н   | Н   | Н  | Х           | Х                | No Operation         | No Operation                                   | 3     |

|                  | Н  | Х   | Х   | Х  | Х           | Х                | Device Deselect      | No Operation or Power<br>Down                  | 3     |

|                  | L  | L   | L   | L  |             | OP CODE          | Mode Register Set    | ILLEGAL                                        | 13    |

|                  | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh | ILLEGAL                                        | 13    |

|                  | L  | L   | Н   | L  | BA          | Х                | Precharge            | Precharge                                      | 7     |

|                  | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate        | ILLEGAL                                        | 4     |

| Row<br>Active    | L  | Н   | L   | L  | ВА          | Col Add.<br>A10  | Write/WriteAP        | Start Write : optional<br>AP(A10=H)            | 6     |

|                  | L  | Н   | L   | Н  | ВА          | Col Add.<br>A10  | Read/ReadAP          | Start Read : optional<br>AP(A10=H)             | 6     |

|                  | L  | Н   | Н   | Н  | Х           | Х                | No Operation         | No Operation                                   |       |

|                  | Н  | Х   | Χ   | Χ  | Х           | Х                | Device Deselect      | No Operation                                   |       |

|                  | L  | L   | L   | L  |             | OP CODE          | Mode Register Set    | ILLEGAL                                        | 13    |

|                  | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh | ILLEGAL                                        | 13    |

|                  | L  | L   | Н   | L  | ВА          | Х                | Precharge            | Termination Burst: Start the Precharge         |       |

| Read             | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate        | ILLEGAL                                        | 4     |

|                  | L  | Н   | L   | L  | ВА          | Col Add.<br>A10  | Write/WriteAP        | Termination Burst: Start<br>Write(optional AP) | 8,9   |

|                  | L  | Н   | L   | Н  | ВА          | Col Add.<br>A10  | Read/ReadAP          | Termination Burst: Start<br>Read(optional AP)  | 8     |

|                  | L  | Н   | Н   | Н  | Х           | Х                | No Operation         | Continue the Burst                             |       |

## CURRENT STATE TRUTH TABLE (Sheet 2 of 4)

| Current                                             |    |     |     |    | С           | ommand           |                      |                                                |       |

|-----------------------------------------------------|----|-----|-----|----|-------------|------------------|----------------------|------------------------------------------------|-------|

| Read with Auto Precharge  Write with Auto Precharge | cs | RAS | CAS | WE | BAO/<br>BA1 | A <i>max</i> -A0 | Description          | Action                                         | Notes |

| Read                                                | Н  | Χ   | Х   | Χ  | Х           | Х                | Device Deselect      | Continue the Burst                             |       |

|                                                     | L  | L   | L   | L  |             | OP CODE          | Mode Register Set    | ILLEGAL                                        | 13    |

|                                                     | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh | ILLEGAL                                        | 13    |

|                                                     | L  | L   | Н   | L  | BA          | Х                | Precharge            | Termination Burst: Start the Precharge         | 10    |

|                                                     | L  | L   | Н   | Н  | ВА          | Row Add.         | Bank Activate        | ILLEGAL                                        | 4     |

| Write                                               | L  | Н   | L   | L  | BA          | Col Add.<br>A10  | Write/WriteAP        | Termination Burst: Start<br>Write(optional AP) | 8     |

|                                                     | L  | Н   | L   | Н  | ВА          | Col Add.<br>A10  | Read/ReadAP          | Termination Burst: Start<br>Read(optional AP)  | 8,9   |

|                                                     | L  | Н   | Н   | Н  | Х           | Х                | No Operation         | Continue the Burst                             |       |

|                                                     | Н  | Х   | Χ   | Χ  | Х           | Х                | Device Deselect      | Continue the Burst                             |       |

|                                                     | L  | L   | L   | L  |             | OP CODE          | Mode Register Set    | ILLEGAL                                        | 13    |

|                                                     | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh | ILLEGAL                                        | 13    |

|                                                     | L  | L   | Н   | L  | BA          | Х                | Precharge            | ILLEGAL                                        | 4,12  |

|                                                     | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate        | ILLEGAL                                        | 4,12  |

|                                                     | L  | Н   | L   | L  | ВА          | Col Add. A10     | Write/WriteAP        | ILLEGAL                                        | 12    |

|                                                     | L  | Н   | L   | Н  | BA          | Col Add. A10     | Read/ReadAP          | ILLEGAL                                        | 12    |

|                                                     | L  | Н   | Н   | Н  | Х           | Х                | No Operation         | Continue the Burst                             |       |

|                                                     | Н  | Χ   | Х   | Χ  | Х           | Х                | Device Deselect      | Continue the Burst                             |       |

|                                                     | L  | L   | L   | L  |             | OP CODE          | Mode Register Set    | ILLEGAL                                        | 13    |

|                                                     | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh | ILLEGAL                                        | 13    |

| Muito with                                          | L  | L   | Н   | L  | BA          | Х                | Precharge            | ILLEGAL                                        | 4,12  |

| Auto                                                | L  | L   | Н   | Н  | ВА          | Row Add.         | Bank Activate        | ILLEGAL                                        | 4,12  |

| Precharge                                           | L  | Н   | L   | L  | BA          | Col Add. A10     | Write/WriteAP        | ILLEGAL                                        | 12    |

|                                                     | L  | Н   | L   | Н  | BA          | Col Add. A10     | Read/ReadAP          | ILLEGAL                                        | 12    |

|                                                     | L  | Н   | Н   | Н  | Χ           | Х                | No Operation         | Continue the Burst                             |       |

|                                                     | Н  | Χ   | Χ   | Χ  | Х           | Х                | Device Deselect      | Continue the Burst                             |       |

## CURRENT STATE TRUTH TABLE (Sheet 3 of 4)

| Commont                                 |    |     |     |    | С           | ommand           |                       |                                         |             |

|-----------------------------------------|----|-----|-----|----|-------------|------------------|-----------------------|-----------------------------------------|-------------|

| Current<br>State                        | cs | RAS | CAS | WE | BAO/<br>BA1 | A <i>max</i> -A0 | Description           | Action                                  | Notes       |

|                                         | L  | L   | L   | L  |             | OP CODE          | Mode Register Set     | ILLEGAL                                 | 13          |

|                                         | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh  | ILLEGAL                                 | 13          |

|                                         | L  | L   | Н   | L  | BA          | Х                | Precharge             | No Operation:<br>Bank(s) idle after tRP |             |

|                                         | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate         | ILLEGAL                                 | 4,12        |

| Precharging                             | L  | Н   | L   | L  | BA          | Col Add. A10     | Write/WriteAP         | ILLEGAL                                 | 4,12        |

|                                         | L  | Н   | L   | Н  | BA          | Col Add. A10     | Read/ReadAP           | ILLEGAL                                 | 4,12        |

|                                         | L  | Н   | Н   | Н  | Х           | Х                | No Operation          | No Operation:<br>Bank(s) idle after tRP |             |

|                                         | Н  | Х   | Х   | Х  | Х           | Х                | Device Deselect       | No Operation:<br>Bank(s) idle after tRP |             |

|                                         | L  | L   | L   | L  |             | OP CODE          | Mode Register Set     | ILLEGAL                                 | 13          |

|                                         | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh  | ILLEGAL                                 | 13          |

|                                         | L  | L   | Н   | L  | BA          | Х                | Precharge             | ILLEGAL                                 | 4,12        |

| Row                                     | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate         | ILLEGAL                                 | 4,11,1<br>2 |

| Activating                              | L  | Н   | L   | L  | BA          | Col Add. A10     | Write/WriteAP ILLEGAL |                                         | 4,12        |

|                                         | L  | Н   | L   | Н  | BA          | Col Add. A10     | Read/ReadAP           | ILLEGAL                                 | 4,12        |

|                                         | L  | Н   | Н   | Н  | Х           | Х                | No Operation          | No Operation: Row<br>Active after tRCD  |             |

|                                         | Н  | Х   | Х   | Х  | Х           | Х                | Device Deselect       | No Operation: Row<br>Active after tRCD  |             |

|                                         | L  | L   | L   | L  |             | OP CODE          | Mode Register Set     | ILLEGAL                                 | 13          |

|                                         | L  | L   | L   | Н  | Χ           | Х                | Auto or Self Refresh  | ILLEGAL                                 | 13          |

|                                         | L  | L   | Н   | L  | BA          | Х                | Precharge             | ILLEGAL                                 | 4,13        |

| \ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \ | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate         | ILLEGAL                                 | 4,12        |

| Write<br>Recovering                     | L  | Н   | L   | L  | ВА          | Col Add. A10     | Write/WriteAP         | Start Write:<br>Optional AP(A10=H)      |             |

|                                         | L  | Н   | L   | Н  | ВА          | Col Add. A10     | Read/ReadAP           | Start Read: Optional<br>AP(A10=H)       | 9           |

|                                         | L  | Н   | Н   | Н  | Х           | Х                | No Operation          | No Operation:<br>Row Active after tDPL  |             |

## CURRENT STATE TRUTH TABLE (Sheet 4 of 4)

| Current             |    |     |     |    | С           | ommand           |                      |                                            |        |

|---------------------|----|-----|-----|----|-------------|------------------|----------------------|--------------------------------------------|--------|

| State               | cs | RAS | CAS | WE | BAO/<br>BA1 | A <i>max</i> -A0 | Description          | Action                                     | Notes  |

| Write<br>Recovering | Н  | Х   | Х   | Х  | Х           | Х                | Device Deselect      | No Operation:<br>Row Active after tDPL     |        |

|                     | L  | L   | L   | L  |             | OP CODE          | Mode Register Set    | ILLEGAL                                    | 13     |

|                     | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh | ILLEGAL                                    | 13     |

|                     | L  | L   | Н   | L  | BA          | Х                | Precharge            | ILLEGAL                                    | 4,13   |

| Write<br>Recovering | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate        | ILLEGAL                                    | 4,12   |

| with Auto           | L  | Н   | L   | L  | BA          | Col Add. A10     | Write/WriteAP        | ILLEGAL                                    | 4,12   |

| Precharge           | L  | Н   | L   | Н  | BA          | Col Add. A10     | Read/ReadAP          | ILLEGAL                                    | 4,9,12 |

|                     | L  | Н   | Н   | Н  | Х           | х                | No Operation         | No Operation:<br>Precharge after tDPL      |        |

|                     | Н  | Х   | Х   | Х  | Х           | Х                | Device Deselect      | No Operation:<br>Precharge after tDPL      |        |

|                     | L  | L   | L   | L  |             | OP CODE          | Mode Register Set    | ILLEGAL                                    | 13     |

|                     | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh | ILLEGAL                                    | 13     |

|                     | L  | L   | Н   | L  | ВА          | Х                | Precharge            | ILLEGAL                                    | 13     |

|                     | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate        | ILLEGAL                                    | 13     |

| Refreshing          | L  | Н   | L   | L  | BA          | Col Add. A10     | Write/WriteAP        | ILLEGAL                                    | 13     |

|                     | L  | Н   | L   | Н  | BA          | Col Add. A10     | Read/ReadAP          | ILLEGAL                                    | 13     |

|                     | L  | Н   | Н   | Н  | Х           | х                | No Operation         | No Operation: idle after tRC               |        |

|                     | Н  | Х   | Х   | Х  | Х           | Х                | Device Deselect      | No Operation: idle after tRC               |        |

|                     | L  | L   | L   | L  |             | OP CODE          | Mode Register Set    | ILLEGAL                                    | 13     |

|                     | L  | L   | L   | Н  | Х           | Х                | Auto or Self Refresh | ILLEGAL                                    | 13     |

|                     | L  | L   | Н   | L  | BA          | Х                | Precharge            | ILLEGAL                                    | 13     |

| Mode                | L  | L   | Н   | Н  | BA          | Row Add.         | Bank Activate        | ILLEGAL                                    | 13     |

| Register            | L  | Н   | L   | L  | BA          | Col Add. A10     | Write/WriteAP        | ILLEGAL                                    | 13     |

| Accessing           | L  | Н   | L   | Н  | BA          | Col Add. A10     | Read/ReadAP          | ILLEGAL                                    | 13     |

|                     | L  | Н   | Н   | Н  | Х           | Х                | No Operation         | No Operation:<br>idle after 2 clock cycles |        |

|                     | Н  | Х   | Х   | Х  | Х           | Х                | Device Deselect      | No Operation:<br>idle after 2 clock cycles |        |

#### Note:

- 1. H: Logic High, L: Logic Low, X: Don't care, BA: Bank Address, AP: Auto Precharge.

- 2. All entries assume that CKE was active during the preceding clock cycle.

- 3. If both banks are idle and CKE is inactive, then in power down cycle

- 4. Illegal to bank in specified states. Function may be legal in the bank indicated by Bank Address, depending on the state of that bank.

- 5. If both banks are idle and CKE is inactive, then Self Refresh mode.

- 6. Illegal if tRCD is not satisfied.

- 7. Illegal if tRAS is not satisfied.

- 8. Must satisfy burst interrupt condition.

- 9. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 10. Must mask preceding data which don't satisfy tDPL.

- 11. Illegal if tRRD is not satisfied

- 12. Illegal for single bank, but legal for other banks in multi-bank devices.

- 13. Illegal for all banks.

## CKE Enable(CKE) Truth TABLE (Sheet 2 of 1)

| Current       | Ск                | Œ                |    |     | Com | mand |             |      |                                        |       |   |                       |   |

|---------------|-------------------|------------------|----|-----|-----|------|-------------|------|----------------------------------------|-------|---|-----------------------|---|

| State         | Previous<br>Cycle | Current<br>Cycle | cs | RAS | CAS | WE   | BAO,<br>BA1 | ADDR | Action                                 | Notes |   |                       |   |

|               | Н                 | Х                | Х  | Х   | Х   | Х    | Х           | Х    | INVALID                                | 1     |   |                       |   |

|               | L                 | Н                | Н  | Х   | Х   | Х    | Х           | Х    | Exit Self Refresh with Device Deselect | 2     |   |                       |   |

| Self          | L                 | Н                | L  | Н   | Н   | Н    | Х           | Х    | Exit Self Refresh with No Operation    | 2     |   |                       |   |

| Refresh       | L                 | Н                | L  | Н   | Н   | L    | Х           | Х    | ILLEGAL                                | 2     |   |                       |   |

|               | L                 | Н                | L  | Н   | L   | Х    | Х           | Х    | ILLEGAL                                | 2     |   |                       |   |

|               | L                 | Н                | L  | L   | Х   | Х    | Х           | Х    | ILLEGAL                                | 2     |   |                       |   |

|               | L                 | L                | Χ  | Х   | Х   | Х    | Х           | Х    | Maintain Self Refresh                  |       |   |                       |   |

|               | Н                 | Х                | Х  | Х   | Х   | Х    | Х           | Х    | INVALID                                | 1     |   |                       |   |

|               |                   | 1                | L  |     | Н   | Н    | Х           | Х    | Х                                      | Х     | Х | Power Down mode exit, | 2 |

| _             |                   | - 11             | L  | Н   | Н   | Н    | Х           | Х    | all banks idle                         | 2     |   |                       |   |

| Power<br>Down | L                 |                  |    | L   | Χ   | Х    | Х           | Х    |                                        |       |   |                       |   |

|               |                   | Н                | L  | Х   | L   | Х    | Х           | Х    | ILLEGAL                                | 2     |   |                       |   |

|               |                   |                  |    |     | Х   | Х    | L           | Х    | Х                                      |       |   |                       |   |

|               | L                 | L                | Х  | Х   | Х   | Х    | Х           | Х    | Maintain Power Down Mode               |       |   |                       |   |

|               | Н                 | Н                | Н  | Х   | Х   | Х    |             |      | Refer to the idle State section        | 3     |   |                       |   |

|               | Н                 | Н                | L  | Н   | Χ   | Х    |             |      | of the Current State                   | 3     |   |                       |   |

|               | Н                 | Н                | L  | L   | Н   | Х    |             |      | Truth Table                            | 3     |   |                       |   |

|               | Н                 | Н                | L  | L   | L   | Н    | Х           | Х    | Auto Refresh                           |       |   |                       |   |

| All           | Н                 | Н                | L  | L   | L   | L    | OP (        | CODE | Mode Register Set                      | 4     |   |                       |   |

| Banks         | Н                 | L                | Н  | Х   | Х   | Х    |             |      | Refer to the idle State section        | 3     |   |                       |   |

| Idle          | Н                 | L                | L  | Н   | Χ   | Х    |             |      | of the Current State                   | 3     |   |                       |   |

|               | Н                 | L                | L  | L   | Н   | Х    |             |      | Truth Table                            | 3     |   |                       |   |

|               | Н                 | L                | L  | L   | L   | Н    | Х           | Х    | Entry Self Refresh                     | 4     |   |                       |   |

|               | Н                 | L                | L  | L   | L   | L    | OP (        | CODE | Mode Register Set                      |       |   |                       |   |

|               | L                 | Х                | Χ  | Х   | Х   | Х    | Х           | Х    | Power Down                             | 4     |   |                       |   |

## CKE Enable(CKE) Truth TABLE (Sheet 2 of 2)

| Current                           | СК                | Œ                |    |     | Com | mand |             |      |                                                            |       |

|-----------------------------------|-------------------|------------------|----|-----|-----|------|-------------|------|------------------------------------------------------------|-------|

| State                             | Previous<br>Cycle | Current<br>Cycle | cs | RAS | CAS | WE   | BAO,<br>BA1 | ADDR | Action                                                     | Notes |

|                                   | Н                 | Н                | Х  | Х   | Х   | Х    | Х           | Х    | Refer to operations of<br>the Current State<br>Truth Table |       |

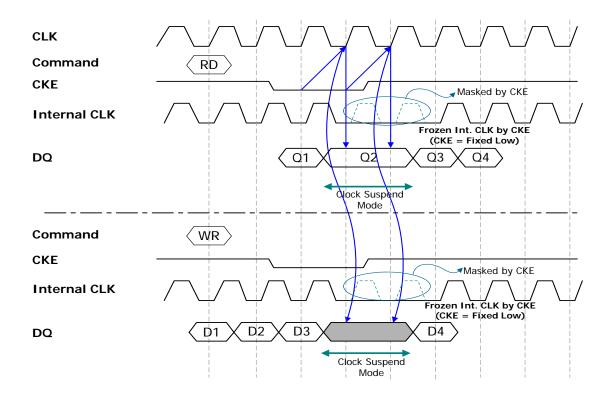

| Any State other than listed above | Н                 | L                | Х  | Х   | Х   | Х    | Х           | Х    | Begin Clock Suspend<br>next cycle                          |       |

| listed above                      | L                 | Н                | Χ  | Х   | Х   | Х    | Х           | Х    | Exit Clock Suspend<br>next cycle                           |       |

|                                   | L                 | L                | Χ  | Х   | Х   | Х    | Х           | Х    | Maintain Clock Suspend                                     |       |

#### Note:

- 1. For the given current state CKE must be low in the previous cycle.

- 2. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. When exiting power down mode, a NOP (or Device Deselect) command is required on the first positive edge of clock after CKE goes high.

- 3. The address inputs depend on the command that is issued.

- 4. The Precharge Power Down mode, the Self Refresh mode, and the Mode Register Set can only be entered from the all banks idle state.

- 5. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. When exiting deep power down mode, a NOP (or Device Deselect) command is required on the first positive edge of clock after CKE goes high and is maintained for a minimum 200usec.

## ициіх

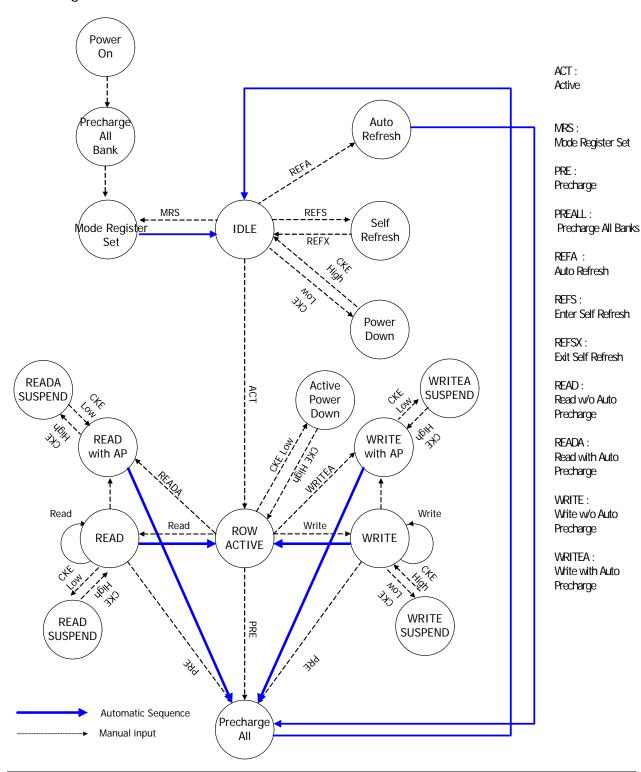

#### **Mobile SDR SDRAM OPERATION**

State Diagram

#### **DESELECT**

The DESELECT function  $\overline{(CS)}$  = High) prevents new commands from being executed by the SDRAM, the SDRAM ignore command input at the clock. However, the internal status is held. The Synchronous DRAM is effectively deselected. Operations already in progress are not affected.

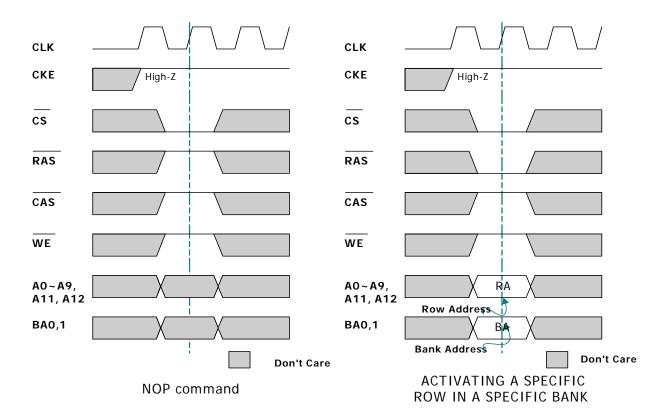

#### NO OPERATION

The NO OPERATION (NOP) command is used to perform a NOP to a SDRAM that is selected  $\overline{(CS)} = Low$ ,  $\overline{RAS} = \overline{CAS} = \overline{WE} = High$ ). This command is not an execution command. However, the internal operations continue. This prevents unwanted commands from being registered during idle or wait states. Operations already in progress are not affected. (see to next figure)

#### **ACTIVE**

The Active command is used to activate a row in particular bank for a subsequent Read or Write access. The value of the BAO,BA1 inputs selects the bank, and the address provided on AO-A12(or the highest address bit) selects the row. This row remains active (or open) for accesses until a PRECHARGE command is issued to that bank. (see to next figure)

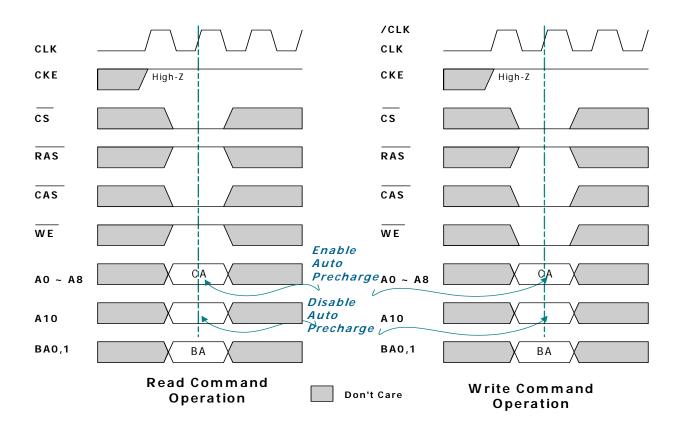

#### READ / WRITE COMMAND

Before executing a read or write operation, the corresponding bank and the row address must be activated by the bank active (ACT) command. An interval of tRCD is required between the bank active command input and the following read/write command input.

The READ command is used to initiate a Burst Read to an active row. The value of BAO and BA1 selects the bank and address inputs select the starting column location.

The value of A10 determines whether or not auto precharge is used. If auto-precharge is selected, the row being accessed will be precharged at the end of the read burst; if auto precharge is not selected, the row will remain open for subsequent access. The valid data-out elements will be available CAS latency after the READ command is issued.

The WRITE command is used to initiate a Burst Write access to an active row. The value of BAO, BA1 selects the bank and address inputs select the starting column location.

The value of A10 determines whether or not auto precharge is used. If auto-precharge is selected, the row being accessed will be precharged at the end of the write burst; if auto precharge is not selected, the row will remain open for subsequent access.

READ / WRITE COMMAND

#### **READ**

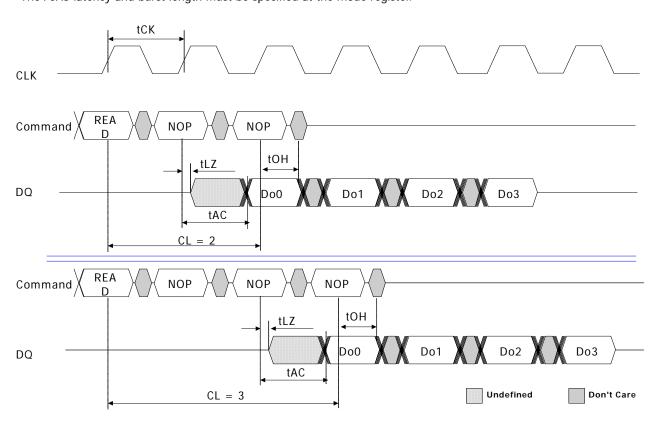

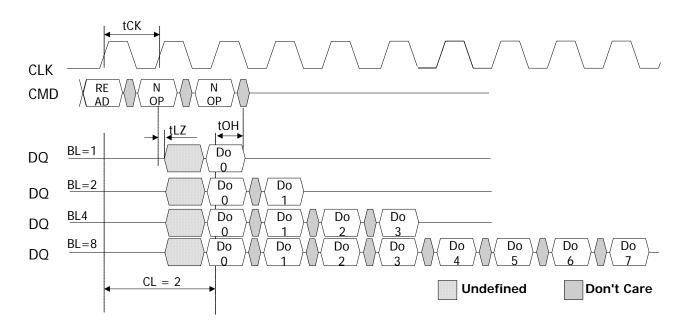

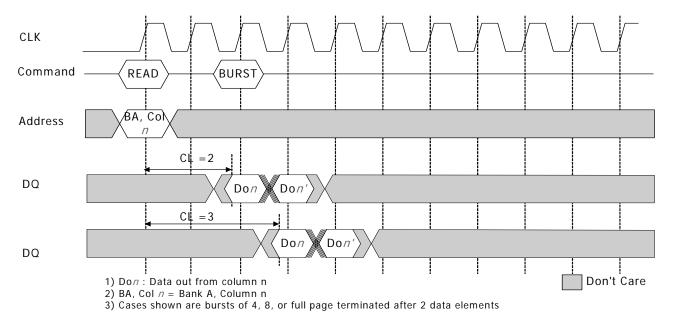

A read operation starts when a read command is input. Output buffer becomes Low-Z in the (/CAS Latency - 1) cycle after read command set. The SDRAM can perform a burst read operation.

The burst length can be set to 1, 2, 4 and 8. The start address for a burst read is specified by the column address and the bank select address at the read command set cycle. In a read operation, data output starts after the number of clocks specified by the /CAS Latency. The /CAS Latency can be set to 2 or 3.

When the burst length is 1, 2, 4 and 8 the DOUT buffer automatically becomes High-Z at the next clock after the successive burst-length data has been output.

The /CAS latency and burst length must be specified at the mode register.

Read Burst Showing CAS Latency

Read Burst Showing BL

#### READ to READ

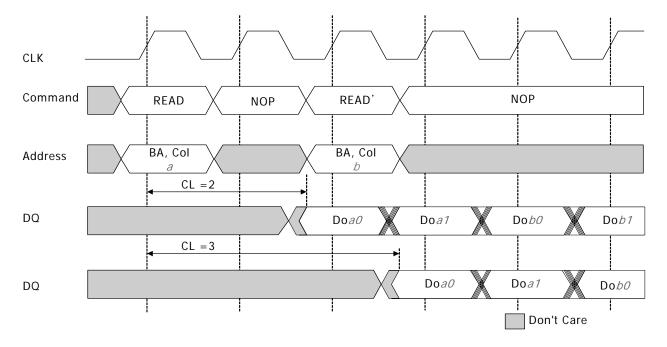

Data from a read burst may be concatenated or truncated by a subsequent READ command. The first data from the new burst follows either the last element of a completed burst or the last desired element of a longer burst that is being truncated.

When another read command is executed at the same ROW address of the same bank as the preceding read command execution, the second read can be performed after an interval of no less than 1 clock. Even when the first command is a burst read that is not yet finished, the data read by the second command will be valid.

Consecutive Read Bursts

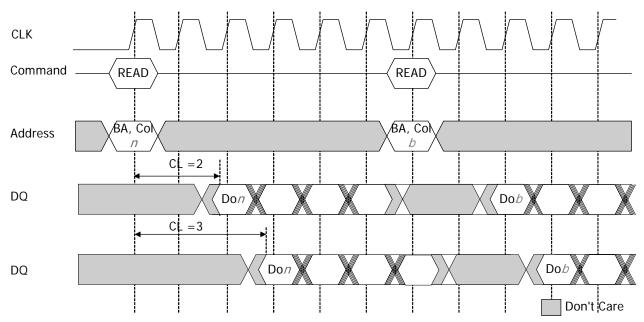

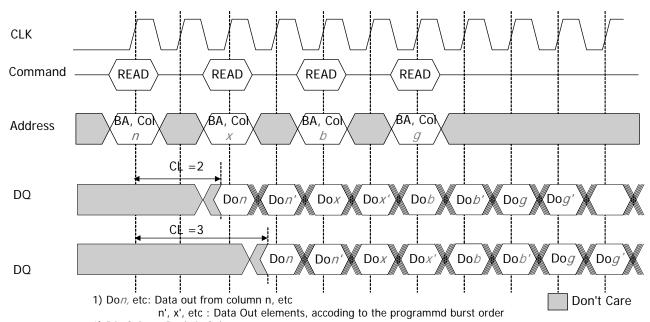

A READ command can be initiated on any clock cycle following a previous READ command. Non-consecutive Reads are shown in Figure. Full-speed random read accesses within a page or pages can be performed as shown in Fig.

- 1) Don (or b): Data out from column n

- 2) BA, Col n(b) = Bank A, Column n (b)

- 3) Burst Length = 4:3 subsequent elements of Data Out appear in the programmed order following Do n (b)

#### Non-Consective Read Bursts

- 2) BA, Col n = Bank A, Column n

- 3) Burst Length = 1, 2, 4, 8 or full page in cases shown

- 4) Read are to active row in any banks

#### Randum Read Bursts

#### **READ BURST TERMINATE**

Data from any READ burst may be truncated with a BURST TERMINATE command. The BURST TERMINATE latency is equal to the read (CAS) latency, i.e., the BURST TERMINATE command should be issued X cycles after the READ command where X equals the desired data-out element.

Terminating a Read Burst

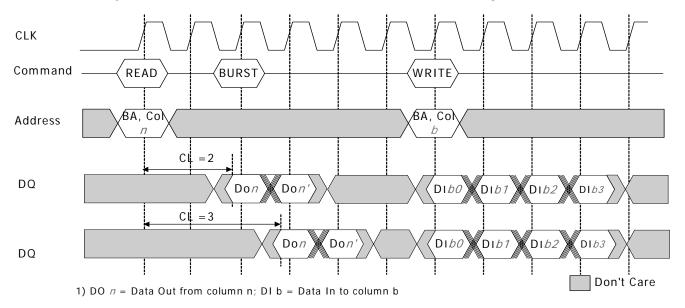

#### **READ to WRITE**

Data from READ burst must be completed or truncated before a subsequent WRITE command can be issued. If truncation is necessary, the BURST TERMINATE command must be used, as shown in next fig.

#### Read to Write

#### Note:

- 1. Same bank, same ROW address: When the write command is executed at the same ROW address of the same bank as the preceding read command, the write command can be performed after an interval of no less than 1 clock. However, DQM must be set High so that the output buffer becomes High-Z before data input.

- 2. Same bank, different ROW address: When the ROW address changes, consecutive write commands cannot be executed; it is necessary to separate the two commands with a precharge command and a bank active command.

- 3. Different bank: When the bank changes, the write command can be performed after an interval of no less than 1 cycle, provided that the other bank is in the bank active state. However, DQM must be set High so that the output buffer becomes High-Z before data input.

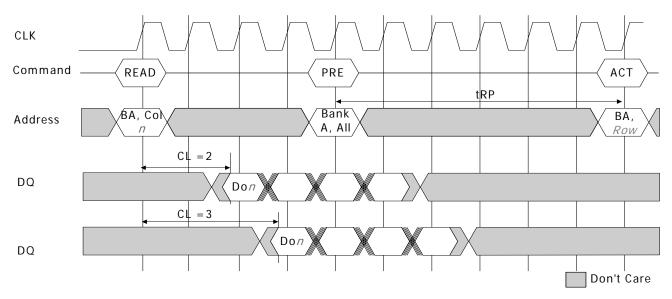

#### READ to PRECHARGE

Following the PRECHARGE command, a subsequent command to the same bank cannot be issued until tRP is met. Note that part of the row precharge time is hidden during the access of the last data element(s).

In the case of a fixed-length burst being executed to completion, a PRECHARGE command issued at the optimum time (as described above) provides the same operation that would result from the same fixed-length burst with auto precharge.

The disadvantage of the PRECHARGE command is that it requires that the command and address buses be available at the appropriate time to issue the command; the advantage of the PRECHARGE command is that it can be used to truncate fixed-length or full-page bursts.

- 1) DO n = Data Out from column n

- 2) Note that Precharge may not be issued before tRAS ns after the ACTIVE command for applicable banks.

- 3) The ACTIVE command may be applied if tRC has been met.

#### **READ to PRECHARGE**

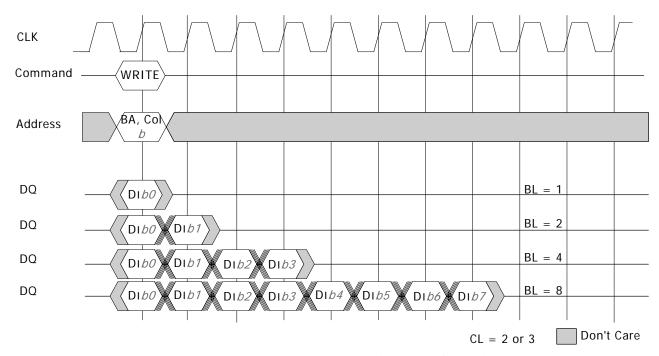

#### Write

Input data appearing on the data bus, is written to the memory array subject to the DM input logic level appearing coincident with the data. If a given DM signal is registered Low, the corresponding data will be written to the memory; if the DM signal is registered High, the corresponding data inputs will be ignored, and a write will not be executed to that byte / column location.

During WRITE bursts, the first valid data-in element will be registered coincident with the WRITE command. Subsequent data elements will be registered on each successive positive clock edge. Upon completion of a fixed-length burst, assuming no other commands have been initiated, the DQ will remain High-Z and any additional input data will be ignored. A full-page burst will continue until terminated.

Data for any WRITE burst may be truncated with a subsequent WRITE command, and data for a fixed-length WRITE burst may be immediately followed by data for a WRITE command. The new WRITE command can be issued on any clock following the previous WRITE command, and the data provided coincident with the new command applies to the new command.

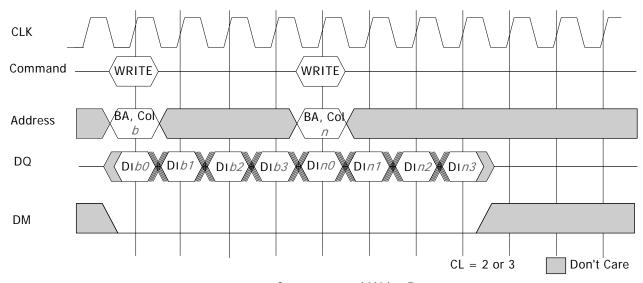

Basic Write timing parameters for Write Burst Operation

#### Note:

- 1. Same bank, same ROW address: When another write command is executed at the same ROW address of the same bank as the preceding write command, the second write can be performed after an interval of no less than 1 clock. In the case of burst writes, the second write command has priority.

- 2. Same bank, different ROW address: When the ROW address changes, consecutive write commands cannot be executed; it is necessary to separate the two write commands with a precharge command and a bank active command.

- 3. Different bank: When the bank changes, the second write can be performed after an interval of no less than 1 clock, provided that the other bank is in the bank active state. In the case of burst write, the second write command has priority.

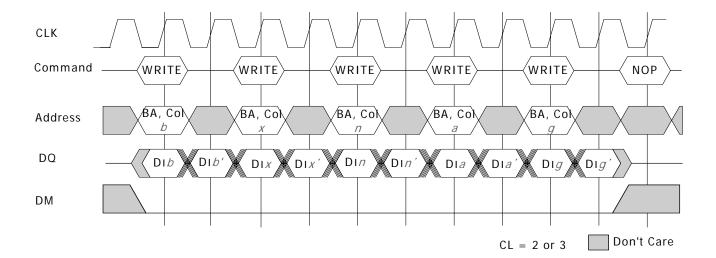

#### WRITE to WRITE

Data for any WRITE burst may be concatenated with or truncated with a subsequent WRITE command. In either case, a continuous flow of input data, can be maintained. The new WRITE command can be issued on any positive edge of the clock following the previous WRITE command. The first data-in element from the new burst is applied after either the last element of a completed burst or the last desired data element of a longer burst which is being truncated. The new WRITE command should be issued X cycles after the first WRITE command, where X equals the number of desired data-in element.

Concatenated Write Bursts

Random Write Cycles

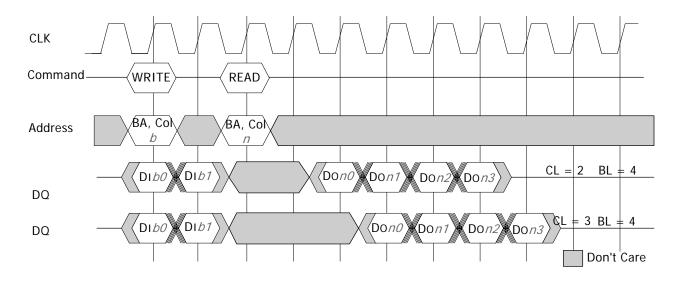

#### WRITE to READ

The preceding burst write operation can be aborted and a new burst read operation can be started by inputting a new read command in the write cycle. The data of the read command (READ) is output after the lapse of the /CAS latency. The preceding write operation (WRIT) writes only the data input before the read command. The data bus must go into a high-impedance state at least one cycle before output of the latest data.

#### Note:

- 1. Same bank, same ROW address: When the read command is executed at the same ROW address of the same bank as the preceding write command, the read command can be performed after an interval of no less than 1 clock. However, in the case of a burst write, data will continue to be written until one clock before the read command is executed.

- 2. Same bank, different ROW address: When the ROW address changes, consecutive read commands cannot be executed; it is necessary to separate the two commands with a precharge command and a bank active command.

- 3. Different bank: When the bank changes, the read command can be performed after an interval of no less than 1 clock, provided that the other bank is in the bank active state. However, in the case of a burst write, data will continue to be written until one clock before the read command is executed (as in the case of the same bank and the same address).

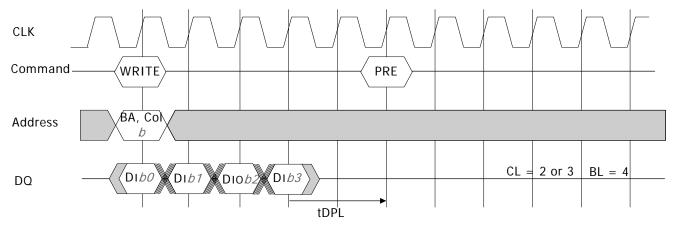

## WRITE to PRECHARGE

Data for any WRITE burst may be followed by a subsequent PRECHARGE command to the same bank (provided Auto Precharge was not activated). When the precharge command is executed for the same bank as the write command that preceded it, the minimum interval between the two commands is 1 clock. However, if the burst write operation is unfinished, the input data must be masked by means of DQM for assurance of the clock defined by tDPL. To follow a WRITE without truncating the WRITE burst, tDPL should be met as shown in Fig.

Non-Interrupting Write to Precharge

Data for any WRITE burst may be truncated by a subsequent PRECHARGE command as shown in Figure. Note that only data-inthat are registered prior to the tDPL period are written to the internal array, and any subsequent data-in should be masked with DM, as shown in next Fig. Following the PRECHARGE command, a subsequent command to the same bank cannot be issued until tRP is met.

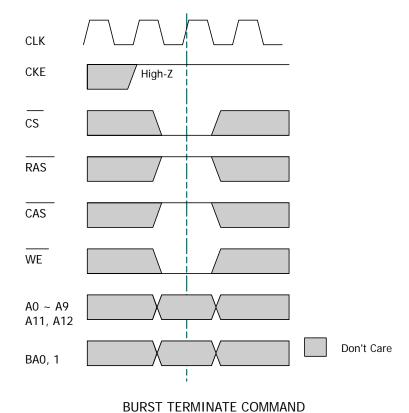

## **BURST TERMINATE**

The BURST TERMINATE command is used to truncate read bursts (with autoprecharge disabled). The most recently registered READ command prior to the BURST TERMINATE command will be truncated, as shown in the Operation section of this datasheet. Note the BURST TERMINATE command is not bank specific. This command should not be used to terminate write bursts.

Rev 1.0 / Sep. 2006 38

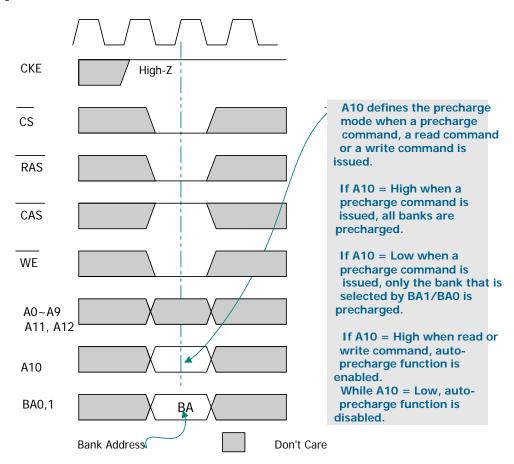

## **PRECHARGE**

The PRECHARGE command is used to deactivate the open row in a particular bank or the open row in all banks. Another command to the same bank (or banks) being precharged must not be issued until the precharge time (trp) is completed.

If one bank is to be precharged, the particular bank address needs to be specified. If all banks are to be precharged, A10 should be set high along with the PRECHARGE command. If A10 is high, BA0 and BA1 are ignored. A PRECHARGE command will be treated as a NOP if there is no open row in that bank, or if the previously open row is already in the process of precharging.

PRECHARGE command

### **AUTO PRECHARGE**

Auto Precharge is a feature which performs the same individual bank precharge function as described above, but without requiring an explicit command.

This is accomplished by using A10 (A10=high), to enable auto precharge in conjunction with a specific Read or Write command. This precharges the bank/row after the Read or Write burst is complete.

Auto precharge is non persistent, so it should be enabled with a Read or Write command each time auto precharge is desired. Auto precharge ensures that a precharge is initiated at the earliest valid stage within a burst.

The user must not issue another command to the same bank until the precharge time (tRP) is completed.

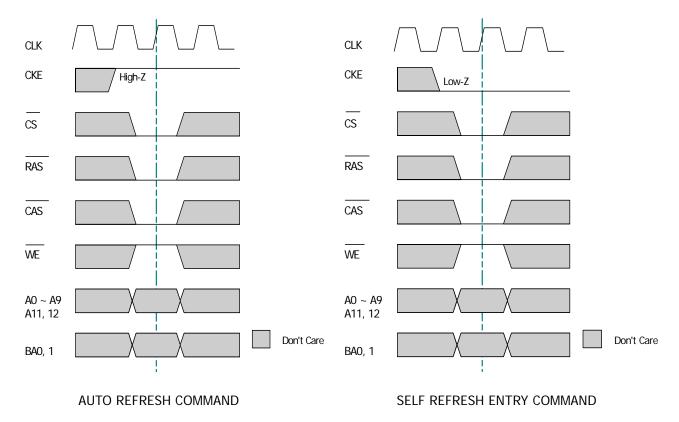

## AUTO REFRESH AND SELF REFRESH

Hynix SDR SDRAM devices require a refresh of all rows in any rolling 64ms interval. Each refresh is generated in one of two ways: by an explicit AUTO REFRESH command, or by an internally timed event in SELF REFRESH mode:

### - AUTO REFRESH.

This command is used during normal operation of the Hynix SDR SDRAM. It is non persistent, so must be issued each time a refresh is required. The refresh addressing is generated by the internal refresh controller. The Hynix SDR SDRAM requires AUTO REFRESH commands at an average periodic interval of tREF.

To allow for improved efficiency in scheduling and switching between tasks, some flexibility in the absolute refresh interval is provided. A maximum of eight AUTO REFRESH commands can be posted to any given SDR SDRAM, and the maximum absolute interval between any AUTO REFRESH command and the next AUTO REFRESH command is 8\*tREF.

#### -SELF REFRESH.

The Self Refresh command is initiated like an Auto Refresh command except CKE is disabled(Low). This state retains data in the SDR SDRAM, even if the rest of the system is powered down. Note refresh interval timing while in Self Refresh mode is scheduled internally in the SDR SDRAM and may vary and may not meet tREF time. After executing a self-refresh command, the self-refresh operation continues while CKE is held Low. During selfrefresh operation, all ROW addresses are refreshed by the internal refresh timer. A self-refresh is terminated by a self-refresh

After executing a self-refresh command, the self-refresh operation continues while CKE is held Low. During selfrefresh operation, all ROW addresses are refreshed by the internal refresh timer. A self-refresh is terminated by a self-refresh exit command. Before and after self-refresh mode, execute auto-refresh to all refresh addresses in or within tREF (max.) period on the condition 1 and 2 below.

- 1. Enter self-refresh mode within time as below\* after either burst refresh or distributed refresh at equal interval to all refresh addresses are completed.

- 2. Start burst refresh or distributed refresh at equal interval to all refresh addresses within time as below\*after exiting from self-refresh mode.

Note: tREF (max.) / refresh cycles.

The use of SELF REFRESH mode introduces the possibility that an internally timed event can be missed when CKE is raised for exit from self refresh mode. Upon exit from SELF REFRESH an extra AUTO REFRESH command is recommended. The Self Refresh command is used to retain cell data in the SDR SDRAM. In the Self Refresh mode, the SDR SDRAM operates refresh cycle asynchronously.

Note 1: If all banks are in the idle status and CKE is inactive (low level), the self refresh mode is set.

| Function           | CKEn-1 | CKEn | cs | RAS | CAS | WE | DQM | ADDR | A10/AP | ВА |

|--------------------|--------|------|----|-----|-----|----|-----|------|--------|----|

| Auto Refresh       | Н      | Н    | L  | L   | L   | Н  | Х   | Х    |        |    |

| Self Refresh Entry | Н      | L    | L  | L   | L   | Н  | Х   | X    |        |    |

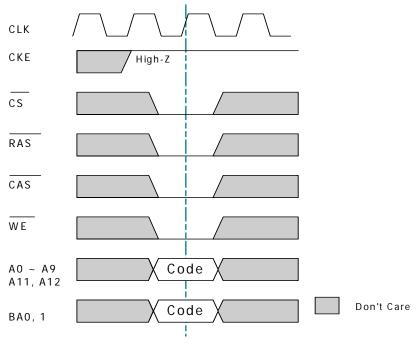

## MODE REGISTER SET

The mode registers are loaded via the address bits.

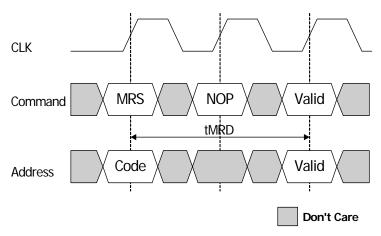

BAO and BA1 are used to select the Mode Register. See the Mode Register description in the register definition section. The MODE REGISTER SET command can only be issued when all banks are idle and no bursts are in progress, and a subsequent executable command cannot be issued until tMRD is met.

MODE REGISTER SET COMMAND

Note:

BA0=BA1=Low loads the Mode Register.

Code = Mode Register / Extended Mode Register selection (BAO, BA1) and op-code (AO - An)

**tMRD DEFINITION**

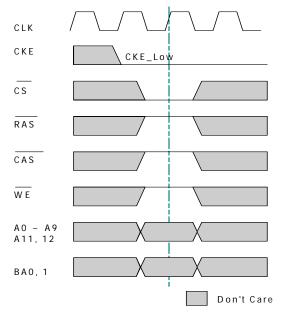

## POWER DOWN

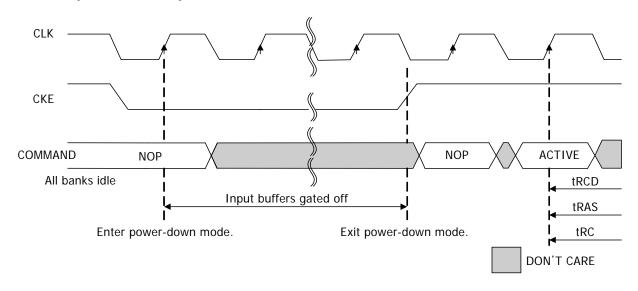

Power down occurs if CKE is set low coincident with Device Deselect or NOP command and when no accesses are in progress. If power down occurs when all banks are idle, it is Precharge Power Down.

If Power down occurs when one or more banks are Active, it is referred to as Active power down. The device cannot stay in this mode for longer than the refresh requirements of the device, without losing data. The power down state is exited by setting CKE high while issuing a Device Deselect or NOP command.

If power-down occurs when all banks are idle, this mode is referred to as precharge power-down; if power-down occurs when there is a row active in any bank, this mode is referred to as active power-down. Entering power-down deactivates the input and output buffers, excluding CKE, for maximum power savings while in standby.

POWER-DOWN COMMAND

### NOTE:

This case shows CKE low coincident with NO OPERATION.

Alternately POWER DOWN entry can be achieved with CKE low coincident with Device DESELECT.

## **Power Up and Initialization**